Intel Seeks Federal Funding to Sustain Moore’s Law Transistor Scaling

Intel CEO Pat Gelsinger has urged the U.S. government to provide sustained funding for semiconductor research, warning that without it, Moore’s Law—the principle driving transistor density doubling every two years—faces obsolescence. In a December 6, 2025, interview at the New York Times DealBook Summit, Gelsinger highlighted the need for public-private partnerships to match global investments from rivals like TSMC and Samsung. He emphasized that federal support could accelerate innovations in process nodes below 1 nanometer, preserving U.S. leadership in chip design and fabrication.

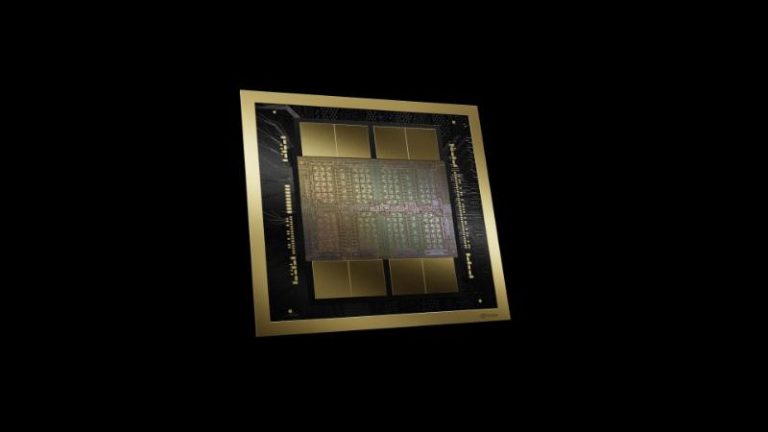

Moore’s Law, first articulated by Intel co-founder Gordon Moore in 1965, has underpinned computing advances for six decades through relentless scaling of silicon transistors. Transistor counts have surged from thousands in early integrated circuits to over 100 billion in modern processors like Intel’s Core Ultra series, enabling exponential gains in performance and efficiency. However, physical limits emerge at atomic scales, where quantum effects degrade signal integrity and increase power leakage. Gelsinger noted that Intel’s 18A process, slated for high-volume production in 2025, incorporates RibbonFET transistors and PowerVia backside power delivery to extend scaling by 15-20% beyond prior generations.

Gelsinger’s call aligns with the CHIPS and Science Act of 2022, which allocated $52 billion for domestic semiconductor manufacturing, including $39 billion in grants and $13 billion for R&D. Intel has received $8.5 billion in preliminary grants for its Arizona, Ohio, and New Mexico fabs, plus $11 billion in loans, funding expansions that will create 20,000 jobs and produce advanced nodes by 2027. Yet Gelsinger argued for a “national mission” akin to NASA’s Apollo program, proposing $100 billion over a decade to fund next-generation lithography and materials science. He cited Europe’s €43 billion European Chips Act and China’s $150 billion semiconductor push as benchmarks, stressing that U.S. underinvestment risks ceding 70% of global foundry capacity to Asia by 2030.

The plea comes amid Intel’s strategic pivot under Gelsinger, who returned as CEO in 2021 to refocus on foundry services. Intel Foundry Direct Connect, launched in 2024, has secured designs from 30 customers, aiming to capture 20% of the $100 billion logic market by 2030. Recent milestones include the Meteor Lake chip’s disaggregated tile architecture and Gaudi 3 accelerators for data centers, though Intel trails AMD and Nvidia in AI workloads. Gelsinger dismissed competitive threats, stating, “We’re not late to the party; we’re building the venue,” while acknowledging a $16.6 billion net loss in Q3 2025 due to foundry ramp-up costs.

Challenges persist in sustaining scaling amid talent shortages and supply chain vulnerabilities. The U.S. produces only 12% of global chips despite designing 53%, per Semiconductor Industry Association data, exacerbating risks from geopolitical tensions like U.S.-China trade restrictions on advanced tools. Gelsinger advocated for visa reforms to attract 50,000 STEM workers annually and tax credits for R&D exceeding 20% of revenues. Initiatives like the National Semiconductor Technology Center, funded at $5 billion under CHIPS, pool resources for co-developed tools, but Gelsinger warned delays in disbursements—averaging 18 months—hinder progress.

Broader implications extend to U.S. economic security, as chips power 90% of modern vehicles, 80% of medical devices, and defense systems. A stalled Moore’s Law could inflate costs by 30% per generation, per IDC forecasts, slowing GDP growth by 0.5% annually. Gelsinger’s testimony before Congress in September 2025 echoed these concerns, linking funding to national defense amid rising cyber and supply threats. Collaborations with DARPA on chiplets and 3D stacking aim to bypass planar limits, targeting 10x density gains by 2030.

Industry peers share the urgency. TSMC’s 1.4nm node, debuting in 2027, uses nanosheet transistors, while Samsung explores 2D materials like graphene for sub-1nm viability. In the U.S., startups like Ayar Labs advance photonic interconnects to reduce latency by 90%, complementing electrical scaling. Gelsinger’s vision positions Intel as a linchpin, leveraging its $25 billion annual R&D budget—largest in the sector—to democratize access via open standards.

Federal response remains pivotal. The Biden administration’s 2025 budget proposes $3 billion for the CHIPS R&D ecosystem, but Gelsinger seeks multiyear commitments to outpace inflation-eroded baselines. As negotiations intensify post-midterms, stakeholders anticipate a revised CHIPS 2.0 bill by Q2 2026, potentially unlocking $20 billion for foundational tech. Sustaining Moore’s Law demands this blend of innovation and policy, ensuring the transistor’s legacy endures for another generation.